1 column

Aliquam gravida nunc id urna eleifend interdum aliquet nulla semper. Vestibulum tempor turpis vel arcu lacinia lacinia.-

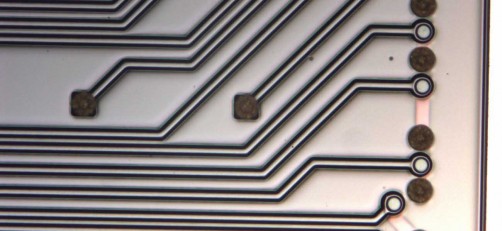

Pad Redistribution (RDL)

RDL Layout Guidelines for wafer level chip scale packaging VIA 1 Repassivation Minimum Opening 30 µm Minimum Overlap (Inside Existing Passivation) 7 µm per side Polyimide Thickness 3 – 5 µm standard Traces Material Standard Thickness Aluminum 2 um (4 um avail) Copper/Nickel 3 um / 2 um Copper (experimental) 3 um Gold 3 um Minimum...

Read Details -

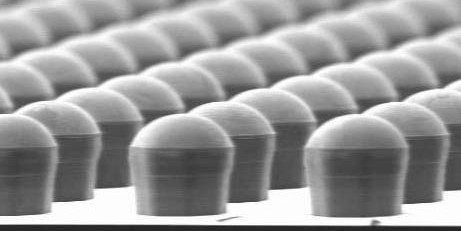

Copper Bumping

Layout Guidelines Copper Bumps (Solder, Nickel, Gold or Indium Cap) 1 Bump Height Average 100 um (10 um to 250 um stacked available) 2 Bump Height Uniformity ±5% (in die); ±15% (in wafer); ±20% (wfr to wfr) 3 Bump Pitch 150 um Standard (Bump Height Dependence) 4 Bump Spacing 75 µm Minimum (Bump Height Dependence) 5...

Read Details -

Indium Bumping

Layout Guidelines Indium Bumps 1 Bump Height Average 35 µm std. (Capability: 5-50 µm) (Bump Size Dependence) 2 Bump Height Uniformity ±10% (in die); ±30% (in wafer); ±30% (wfr to wfr) 3 Bump Pitch 20 µm Minimum (Bump Size Dependence) 4 Bump Spacing 10 µm Minimum 5 Bump to Passivation Overlap 7 µm Per Side Minimum...

Read Details -

Gold Bumping

Layout Guidelines Gold Bumps 1 Bump Height Average 18 µm & 25 µm std. (Capability: 2-50 µm) 2 Bump Height Uniformity ±5% (in die); ±10% (in wfr); ±15% (wfr to wfr) 3 Bump Pitch 50 µm Minimum (bump size dependence) 4 Bump Spacing 18 µm Minimum (bump height dependence) 5 Bump to Passivation Overlap 7 µm Per...

Read Details